Kufa Journal of Engineering Vol. 9, No. 4, October 2018, P.P. 146-162 Received 22 October 2017, accepted 16 January 2018

# COMPARISON BETWEEN LS-PWM AND LPS-PWM FOR SWITCHING-CAPACITOR (SC) INVERTER

Ali K. Abdul-Abbas<sup>1</sup> and Shafaa M. Salih<sup>2</sup>

<sup>1</sup>Department of Electrical Engineering, College of Engineering -Basra University, Iraq. Email: <u>ali\_univbasra75@yahoo.com</u>

<sup>2</sup> Department of Computer Engineering, College of Engineering -Basra University. Iraq. Email: shafaa1976\_21@yahoo.com

http://dx.doi.org/10.30572/2018/kje/090410

### **ABSTRACT:**

A two modulation methods of the switching-capacitor inverter are proposed. The inverter output voltage is larger than the input voltage by connect switching-capacitor in series and in parallel respectively. The level output voltages are decided by number of the capacitor. Five capacitors are used to obtain eleven level in output voltage waveform. The proposed inverter is driven by the LS-PWM and LPS-PWM methods. The circuit configuration, states operation and simulation results by using MATLAB/SIMULINK are presented in this paper. The simulation results demonstrated best LPS-PWM method compared with LS-PWM in terms THD of output voltage.

**KEYWORDS:** inverter, voltage, capacitor, waveform.

#### 1. INTRODUCTION

AC-DC converters with rise voltage gain are desired in considerable industrial applications such as front-end parts for neat energy sources, Uninterruptible Power Supplies (UPS), Electrical Vehicles (EVs), and Distributed Generation (DG) systems (Yoo et al., 2008; Lu et al., 2017). EVs are distinguished by motor drive equipments, where power electronic is used in electric power conversion such as Pulse Width Modulation (PWM) inverters and DC/DC converters (Emadi et al., 2006).

The inverter with a step-up transformer, the Z-source inverter, and single stage flyback inverter are used to obtain high input voltage/ output voltage ratio (Hu et al., 2017; Voglitsis et al., 2017). But the transformer or the inductor creates the inverter which is big because they have large size magnetic cores to bear the high power (Chandrasekaran and Gokdere, 2004).

The multilevel inverter techniques are used a lot of attention because the attractive solution for high power applications. The output voltage of The multilevel inverter is graduate waveform, lower common-mode voltages, reduced (dv/dt) voltage and lower Total Harmonic Distortion (THD) (Franquelo et al., 2008). The multilevel inverter has numerous topologies; such as, the cascade H-bridge (CHB) inverter (Karasani et al., 2017), the Neutral Point Clamped PWM (NPC-PWM) inverter (Rodriguez et al., 2009) and the flying capacitor inverter (Kou et al., 2004). These topologies have a major number of switching device or numerous input voltage sources.

A Switched Capacitor (SC) inverter outputs have higher outputs and large gain ratio in a similar way to the charge pumps (Ardashir et a., 2017). A SC inverter using series and parallel conversion is based on the boost converter and a full-wave bridge inverter (Hinago, and Koizumi, 2010).

The SC inverter has the lower number of devices contrast to the conventional multilevel inverters (Fong et al., 2017). There are numerous modulation methods to drive a SC inverter: the multicarrier PWM (McGrath and Holmes, 2002), the space vector modulation (Das and Narayanan, 2012), the hybrid modulation and the selective harmonic elimination (Agelidis et al., 2008). The Level and Phase Shifted PWM (LPS-PWM) method is incorporation of the Level Shifted PWM (LS-PWM) and Phase Shifted PWM (PS-PWM) (Hinago and Koizumi 2011).

In this paper, four stages of SC inverter driven by LS-PWM and PS-PWM methods are proposed. The voltage ripple and the losses in this inverter are less comparable with

conventional inverters. The operation stage principle and simulation results are shown and compared based on a newly four stage SC inverter.

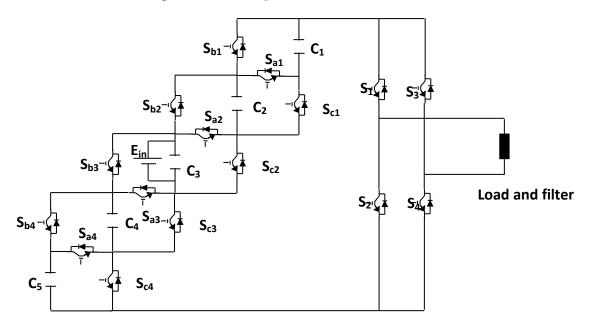

### 2. MODEL DESCRIPTION AND STATE OF OPERATION IN LS-PWM METHOD

A model configuration of the four layer switching-capacitor (SC) inverter is shown in Fig. 1 (Hinago, and Koizumi, 2010). The one phase circuit, switches Sai, Sbi, and Sci (I=1,2,3,4) are used which switch for the capacitors Ch (h=1,2,3,4,5) that connected in parallel to charge and in series to discharge so that the output of the inverter a higher voltage than the input voltage EIN.

The switches Sai are utilized for series attachment of capacitors and switches Sbi and Sci are utilized for parallel attachments of capacitors. The condenser C3 couple in parallel to the supply Ein can be rejected when using ideal voltage source performs. The full-bridge inverter used switches S1-S4 in the output stage and low pass filter is constructed from an inductor L and capacitor C with resistive or inductive loads can be connected in the output terminal of the inverter.

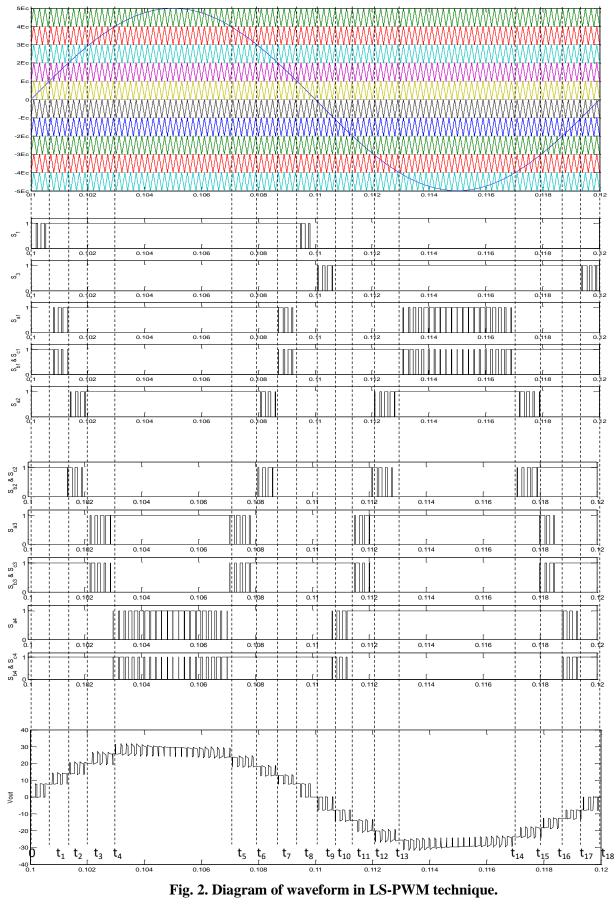

In LS-PWM technique, five stages operation in each half cycle of reference voltage can be described in the following (referred to Fig. 2).

Fig. 1. Proposed diagram of switching capacitor circuit.

### Stage 1

When the time period (t) is satisfied  $(0 \le t \le t_1)$  in Fig. 2, the switches  $S_{ai}$  are turned off by the pulses in gate-source voltage  $V_{GSai}$  but the switches  $S_{bi}$  and  $S_{ci}$  are turned on by the drive in gate-source voltages  $V_{GSbi}$  and  $V_{GSci}$  respectively.

The switches  $S_{bi}$  and  $S_{ci}$  are derived by the same pulses. The switches  $S_1$  and  $S_2$  are turned on or off alternately while the switches  $S_3$  is maintained off states and  $S_4$  is preserved on states. Therefore, the states shown in Fig. 3a and b are transform alternately and the output voltage  $V_{out}$  occupy between 0 and  $E_{in}$ .

### Stage 2

When the condition for time duration is satisfied ( $t_1 \le t \le t_2$ ) in Fig. 2. The upper switches  $S_{a1}$ ,  $S_{b1}$ , and  $S_{c1}$  are switched alternative by the gate-source voltage  $V_{GSa1}$ ,  $V_{GSb1}$ , and  $V_{GSc1}$ , respectively. While the state lower switches  $S_{ai}$  (i=2,3,4) is turned off and  $S_{bi}$  and  $S_{ci}$  (i=2,3,4) are maintained turn on.

The condenser  $C_1$  is charged by the negative current  $i_{C1}$  as shown in Fig. 3(b) and discharged by positive current  $i_{C1}$  as shown in Fig. 3c. So the output voltage satisfied the following relation

$$V_{\text{out}} = E_{\text{in}} + V_{\text{C1}}$$

Where  $V_{C1}$  is the voltage across the capacitor  $C_1$ . Therefore, the output voltage  $V_{out}$  is charging between  $E_{in}$  and  $E_{in} + V_{C1}$ .

### Stage 3

When the period (t) satisfied ( $t_2 \le t \le t_3$ ) in Fig. 2. The switches  $S_{a2}$ ,  $S_{b2}$ , and  $S_{c2}$  are switched on while  $S_{a1}$ ,  $S_{b1}$ , and  $S_{c1}$  are kept on state however  $S_{ai}$  (i=3,4) is kept turn on while  $S_{bi}$  and  $S_{ci}$  (i=3,4) are keep turn off. The condenser  $C_2$  is charged by the negative current  $i_{C2}$  as shown in Fig. 3d and discharged by the positive current  $i_{C2}$ .

The output voltage  $V_{out}$  is

$$V_{out} = E_{in} + V_{C1} + V_{C2}$$

Where  $V_{C2}$  is the potential difference on the capacitor  $C_2$ . Thus, the output voltage is charging between  $E_{in} + V_{C1}$  and  $E_{in} + V_{C1} + V_{C2}$  alternately.

## Stage 4

In the interval ( $t_3 \le t \le t_4$ ), the full-bridge inverter switches  $S_1$  and  $S_4$  is turn on while  $S_2$  and  $S_3$  are turn off.

The switches  $S_{ai}$  (i=1,2) are turned on while  $S_{bi}$  and  $S_{ci}$  (i=1,2) are turn off. However, switches  $S_{a3}$ ,  $S_{b3}$  and  $S_{c3}$  are turned on or off alternately and the switches  $S_{a4}$  is turning off while  $S_{b4}$  and  $S_{c4}$  are turning on. So the capacitor  $C_1$  and  $C_2$  are discharging and capacitor  $C_4$  is charging and discharging alternately while capacitor  $C_5$  is charging as shown in Fig. 3e. In these states, the output voltage  $V_{out}$  change between  $E_{in} + V_{C1} + V_{C2}$  and  $E_{in} + V_{C1} + V_{C2} + V_{C4}$  respectively.

### Stage 5

This stage can be described during the interval which is  $(t_4 \le t \le t_5)$ , the full-wave inverter switches keep of the states and switches  $S_{ai}$  (i=1,2,3) are turned on while switches  $S_{bi}$  and  $S_{ci}$  (i=1,2,3) are turned off. The switches  $S_{a4}$ ,  $S_{b4}$  and  $S_{c4}$  are turned on or off alternately as shown in Fig. 3f.

In this case, the output voltage  $V_{out}$  change between  $E_{in}$  +  $V_{C1}$ +  $V_{C2}$ + $V_{C4}$ . and  $E_{in}$  +  $V_{C1}$ +  $V_{C2}$ + $V_{C4}$ + $V_{C5}$  respectively.

After time ( $t_5$ ), the five states are iterative by a half cycle of reference voltage and illustrated in Table 1. For the positive half cycle of the reference wave and Table.2 in the negative half cycle of the reference wave by purpose  $V_{C1}=V_{C2}=V_{C4}=V_{C5}=E_{in}$ .

Table 1. Positive half cycle of reference wave for  $V_{C1}=V_{C2}=V_{C4}=V_{C5}=E_{in}$

| State | Period                           | $S_{a1} = \overline{S_{b1}} =$ | $S_{a2} = \overline{S_{b2}} =$ | $S_{a3} = \overline{S_{b3}} =$ | $S_{a4} = \overline{S_{b4}} =$ | $S_1 = \overline{S_2}$ | $S_3 = \overline{S_4}$ | $\mathbf{V}_{	ext{out}}$                                                          |

|-------|----------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|------------------------|------------------------|-----------------------------------------------------------------------------------|

|       | of state                         | $\overline{S_{c1}}$            | $\overline{S_{c2}}$            | $\overline{S_{c3}}$            | $\overline{S_{c4}}$            |                        |                        |                                                                                   |

| 1     | 0≤t≤t <sub>1</sub>               | 0                              | 0                              | 0                              | 0                              | 0↔1                    | 0                      | $0 \leftrightarrow E_{in}$                                                        |

| 2     | $t_1 \leq t \leq t_2$            | 0↔1                            | 0                              | 0                              | 0                              | 1                      | 0                      | $E_{in} \!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

| 3     | $t_2 \leq t \leq t_3$            | 1                              | 0↔1                            | 0                              | 0                              | 1                      | 0                      | $2E_{in}\!\!\leftrightarrow 3E_{in}$                                              |

| 4     | $t_3 \leq t \leq t_4$            | 1                              | 1                              | 0↔1                            | 0                              | 1                      | 0                      | $3E_{in}\!\!\leftrightarrow 4E_{in}$                                              |

| 5     | $t_4 \leq t \leq t_5$            | 1                              | 1                              | 1                              | 0↔1                            | 0↔1                    | 0                      | $4E_{in}\!\!\leftrightarrow 5E_{in}$                                              |

| 6     | $t_5 \leq t \leq t_6$            | 1                              | 1                              | 0↔1                            | 0                              | 1                      | 0                      | $3E_{in}\!\!\leftrightarrow 4E_{in}$                                              |

| 7     | t <sub>6</sub> ≤t≤t <sub>7</sub> | 1                              | 0↔1                            | 0                              | 0                              | 1                      | 0                      | $2E_{in}\!\!\leftrightarrow 3E_{in}$                                              |

| 8     | $t_7 \leq t \leq t_8$            | 0↔1                            | 0                              | 0                              | 0                              | 1                      | 0                      | $E_{in} \!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

| 9     | t <sub>8</sub> ≤t≤t <sub>9</sub> | 0                              | 0                              | 0                              | 0                              | 0↔1                    | 0                      | $0 \leftrightarrow E_{in}$                                                        |

| State | Period of                          | $S_{a1} = \overline{S_{b1}} =$ | $S_{a2} = \overline{S_{b2}} =$ | $S_{a3} = \overline{S_{b3}} =$ | $S_{a4} = \overline{S_{b4}} =$ | $S_1 = \overline{S_2}$ | $S_3 = \overline{S_4}$ | V <sub>out</sub>                                                        |

|-------|------------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|------------------------|------------------------|-------------------------------------------------------------------------|

|       | state                              | $\overline{S_{c1}}$            | $\overline{S_{c2}}$            | $\overline{S_{c3}}$            | $\overline{S_{c4}}$            |                        |                        |                                                                         |

| 10    | t <sub>9</sub> ≤t≤t <sub>10</sub>  | 0                              | 0                              | 0                              | 0                              | 0                      | 0↔1                    | 0↔ -E <sub>in</sub>                                                     |

| 11    | $t_{10} \le t \le t_{11}$          | 0                              | 0                              | 0                              | 0↔1                            | 0                      | 1                      | $\text{-}E_{in} \!\! \longleftrightarrow \text{-}2E_{in}$               |

| 12    | $t_{11} \le t \le t_{12}$          | 0                              | 0                              | 0↔1                            | 1                              | 0                      | 1                      | $-E_{in} \leftrightarrow -3E_{in}$                                      |

| 13    | $t_{12} \le t \le t_{13}$          | 0                              | 0↔1                            | 1                              | 1                              | 0                      | 1                      | $-E_{in} \leftrightarrow -4E_{in}$                                      |

| 14    | $t_{13} \le t \le t_{14}$          | 0↔1                            | 1                              | 1                              | 1                              | 0                      | 0↔1                    | $-E_{in} \leftrightarrow -5E_{in}$                                      |

| 15    | $t_{14} \le t \le t_{15}$          | 0                              | 0↔1                            | 1                              | 1                              | 0                      | 1                      | $-E_{in} \leftrightarrow -4E_{in}$                                      |

| 16    | $t_{15} \leq t \leq t_{16}$        | 0                              | 0                              | 0↔1                            | 1                              | 0                      | 1                      | $-E_{in} \leftrightarrow -3E_{in}$                                      |

| 17    | t <sub>16</sub> ≤t≤t <sub>17</sub> | 0                              | 0                              | 0                              | 0↔1                            | 0                      | 1                      | $\text{-}E_{\text{in}} \!\! \longleftrightarrow \text{-}2E_{\text{in}}$ |

| 18    | $t_{17} \le t \le t_{18}$          | 0                              | 0                              | 0                              | 0                              | 0                      | 0↔1                    | $0 \leftrightarrow -E_{in}$                                             |

Table 2. Negative half cycle of reference wave for  $V_{C1}=V_{C2}=V_{C4}=V_{C5}=E_{in}$

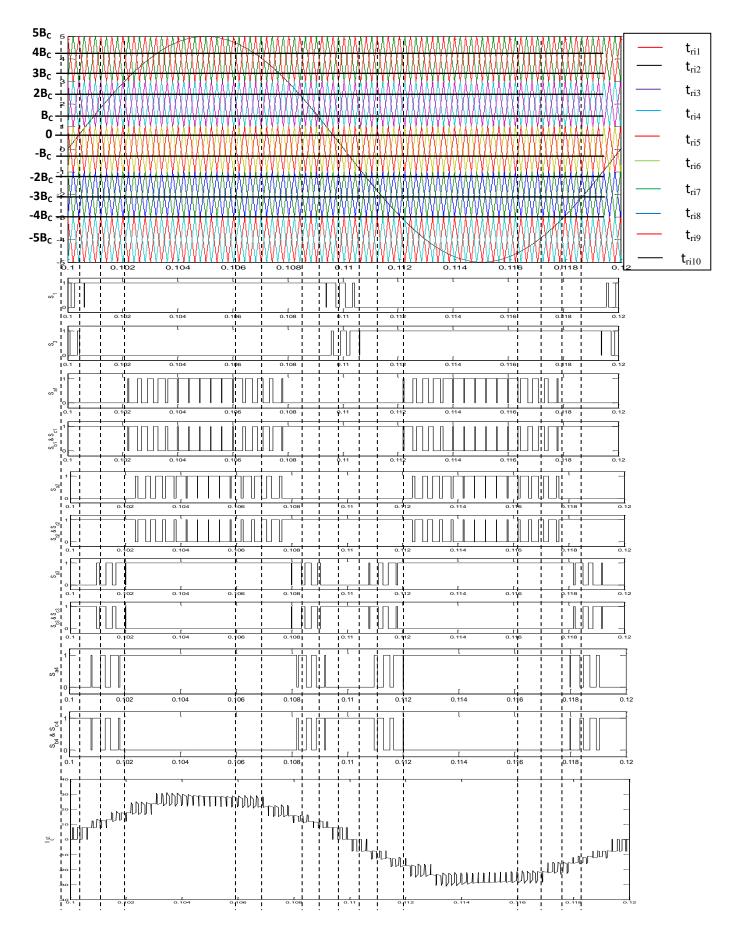

### 3. OPERATION PRINCIPLE OF SC INVERTER IN LPS-PWM METHOD

Fig. 4 illustrates the basic pulse in the LPS-PWM method, the reference waveforms  $e_{ref}$  is splited into five levels. With triangle waveform  $t_{ri1}$  is employed between  $3B_c$  and  $5B_c$ , another triangle waveform  $t_{ri3}$  is employed between  $B_c$  and  $3B_c$ , and triangle  $t_{ri5}$  is employed between -  $3B_c$  and  $-B_c$ , and  $t_{ri9}$  is employed between -  $3B_c$  and -  $3B_c$  respectively. Which are coincide in the same phase at the carrier frequency  $f_{ref}$  and their magnitude of  $B_c$ . The other triangle waveforms  $t_{ri2}$ ,  $t_{ri4}$ ,  $t_{ri6}$ ,  $t_{ri8}$ , and  $t_{ri10}$  are put on each level but their phases are shifted by 180 degree with respect to the previous group so it is called to this modulation as level and phase shifted (LPS).

The operation principle can be described by the following:

- 1- when  $e_{ref} > t_{ri6}$  so  $S_1$  is on and  $S_2$  is off but when  $e_{ref} > t_{ri5}$  so  $S_3$  is on and  $S_4$  is off.

- 2- when  $e_{ref} > t_{ri1}$  and  $e_{ref} < t_{ri9}$  so  $S_{a1}$  is on and  $S_{b1}$ ,  $S_{c1}$  are off.

- 3- when  $e_{ref} > t_{ri2}$  and  $e_{ref} < t_{ri10}$  so  $S_{a2}$  is on and  $S_{b2}$ ,  $S_{c2}$  are off.

- 4- when  $e_{ref} > t_{ri3}$  and  $e_{ref} < t_{ri7}$  so  $S_{a3}$  is on and  $S_{b4}$ ,  $S_{c4}$  are off.

- 5- when  $e_{ref} > t_{ri4}$  and  $e_{ref} < t_{ri8}$  so  $S_{a4}$  is on and  $S_{b3}$ ,  $S_{c3}$  are off.

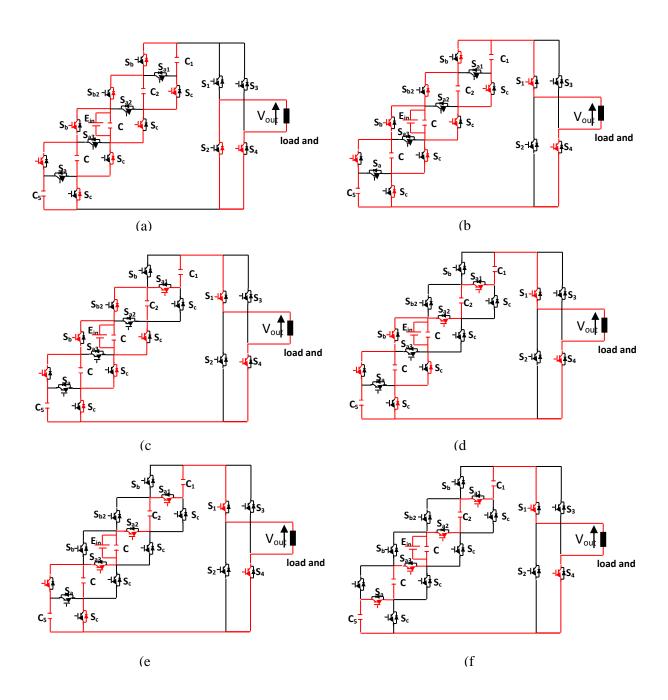

Fig. 3. Proposed diagram of operation in different stage (a)Vout=0 ,(b) Vout=Ein , (c) Vout=Ein+VC1 , (d) Vout=Ein+VC1+VC2 , (e) Vout=Ein+VC1+VC2+VC4 , (f) Vout=Ein+VC1+VC2+VC4+VC5.

Fig. 4. Diagram of waveform in LPS-PWM technique.

# 4. SIMULATION BLOCKS OF LS-PWM AND LPS-PWM TECHNIQUES

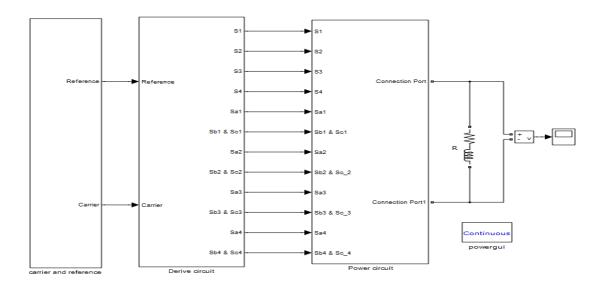

This part is devoted to the simulation block of the switched-capacitor inverter. Simulation diagram is divided into three blocks (as shown in Fig. 5): carrier and reference block, derive circuit and power circuit.

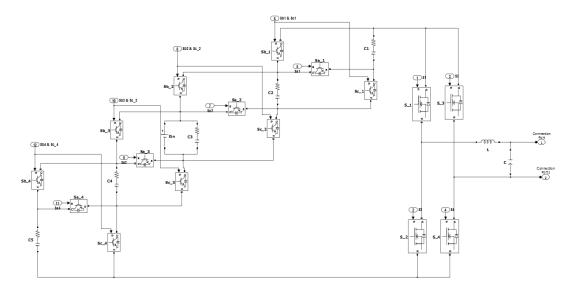

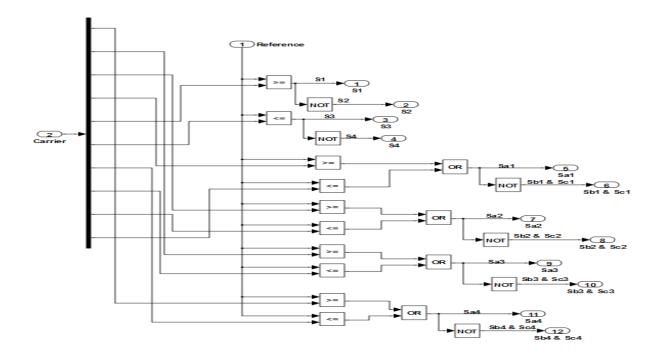

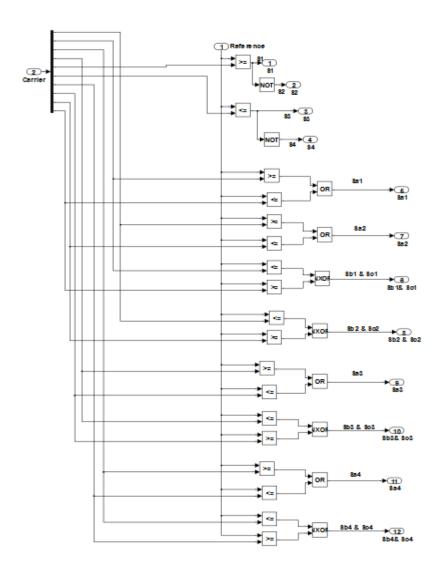

The power circuit is common for both techniques (as shown in Fig. 6), while each drive circuit is specified for certain techniques. The first drive circuit generation pulse for the power circuit using LS-PWM(as shown in Fig. 7), whereas the pulse generation of the second drive circuit is based on LPS-PWM(as shown in Fig. 8). In addition, each technique has its own reference and carrier block.

Fig. 5. Block diagram of SC inverter.

Fig. 6. Block diagram of power circuit.

Fig. 7. Block diagram of drive circuit for LS-PWM technique.

### 5. SIMULATION RESULT

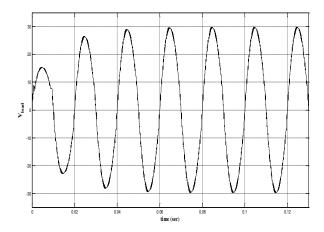

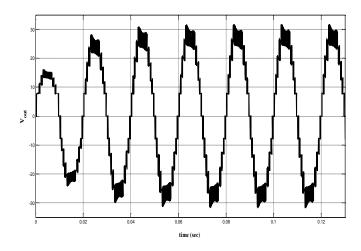

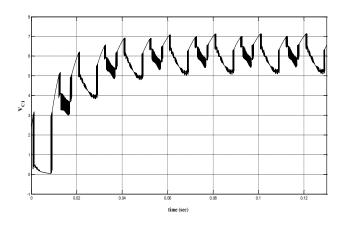

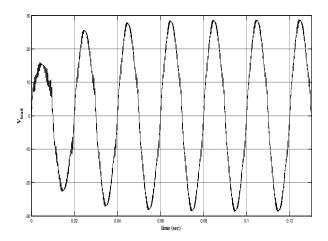

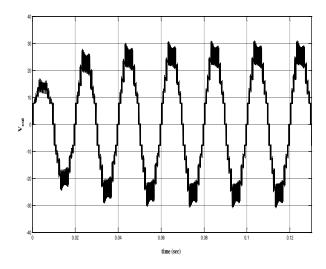

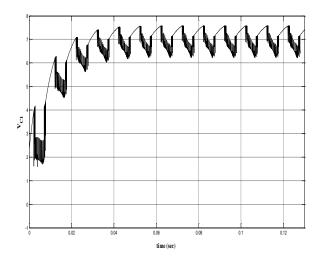

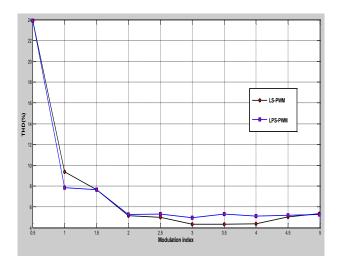

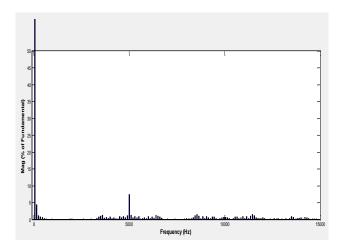

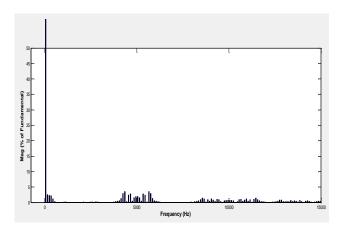

The switched-capacitor inverter is modeled in SIMULINK/MATLAB using power system set. The load voltage after filter, output voltage from inverter and voltage in capacitor C1 for LS-PWM and LPS-PWM techniques are shown in Figs. 9-14. The relation between THD and modulation index as shown in Fig. 15 and harmonic spectrum of two technique are shown in Figs. 16 and 17.

Compared to the results of the two methods in terms of THD shows that the results of the first method best for the modulation index range from 2.5 to 4.5.

The voltage ripple of the capacitor C1 was reduced when the proposed LPS-PWM method was applied compared with LPS-PWM. Therefore, the losses caused by the voltage reduction of the switched capacitors were low and the efficiency of the inverter was improved.

Fig. 8. Block diagram of drive circuit for LPS-PWM technique.

Fig. 9. Load voltage of circuit with LS-PWM technique.

Fig. 10. Output voltage of circuit with LS-PWM technique.

Fig. 11. Capacitor voltage ( $V_{\text{CI}}$ ) of circuit with LS-PWM technique.

Fig. 12. Load voltage of circuit with LPS-PWM technique.

Fig. 13. Output voltage of circuit with LPS-PWM technique.

Fig. 14. Capacitor voltage  $(V_{C1})$  of circuit with LPS-PWM technique.

Fig. 15. THD against modulation index for LS-PWM technique.

Fig. 16. Harmonic distortion of output voltage for LS-PWM technique.

Fig. 17. Harmonic distortion of output voltage for LPS-PWM technique.

## 6. CONCLUSION

In this paper, a switched-capacitor inverter is suggest. The circuit diagram was introduced and the two modulation method (LS-PWM and LPS-PWM) were shown. The circuit stage operation of the suggested inverter was promoted by the simulation results with a resistive and inductive load.

The suggest inverter output shows a great voltage than the input voltage by switching the capacitors in series and in parallel.

The framework of the inverter is simpler than the classical switched-capacitor inverters. THD of the output waveform in LPS-PWM technique is reduced compared to the LS-PWM technique.

#### 7. REFERENCES

Yoo, H., Sul, S. K., Park, Y. and Jeong, J., "System Integration and Power-Flow Management for a Series Hybrid Electric Vehicle Using Supercapacitors and Batteries," IEEE Trans. on Industry applications, vol.44, no. 1, pp. 108-114, Jan./Feb..2008.

Lu, J., Govestan, S., Savaghebi, M., J. Vasquez C. and Guerrero J. M., "An Enhanced State Observer for DC-Link Voltage Control of Three-Phase AC/DC Converters," IEEE Trans. on power electronics, pp. 936-942, July 2017.

Emadi, A., Williamson, S. S., and Khaligh, A., "Power electronics intensive solutions for advanced electric, hybrid electric, and fuel cell vehicular power systems," IEEE Trans. on Power Electron., vol. 21, no. 3, pp. 567–577, May 2006.

Hu, S., Liang, Z. and He, X., "combined current sensing method for the three-phase quasi-z-source inverter," IEEE Trans. on Industrial electronics, vol. 64, Issue 9, pp. 7152-7160, Sept. 2017.

Voglitsis, D., Papanikolaou, N. and Kyritsis, A.," incorporation of harmonic injection in interleaved flyback inverter for the implementation of an active anti-islanding technique", IEEE Trans. on Power Electron., vol. 32, Issue 11, pp. 8526-843, Nov. 2017.

Chandrasekaran, S. and Gokdere, L. U., "Integrated magnetics for interleaved DC–DC boost converter for fuel cell powered vehicles," in Proc. IEEE Power Electron. Spec. Conf., pp. 356–361, Jun. 2004.

Franquelo, L., Rodriguez, J., Leon, J., Kouro, S., Portillo, R., and Prats, M., "The age of multilevel converters arrives," Industrial Electronics Magazine, IEEE, vol. 2, no. 2, pp. 28–39, June 2008.

Karasani, R. R., Borghate, V. B., Meshram, P. M., Suryawanshi, H. M., and Sabyasachi, S., "A three-phase hybrid cascaded modular multilevel inverter for renewable energy environment," IEEE Transactions on Power Electronics, vol. 32, no. 2, pp. 1070–1087, Feb 2017.

Rodriguez, J., Franquelo, L. G., Kouro, S., Leon, J. I., Portillo, R. C., Prats, M. A. M., and Perez, M. A., "Multilevel converters: An enabling technology for high-power applications," Proc. IEEE, vol. 97, no. 11, pp. 1786–1817, Nov. 2009.

Kou, X., Corzine, Familiant, K. A., and Y. L., "A unique fault-tolerant design for flying capacitor multilevel inverter," IEEE Trans. Power Electron., vol. 19, no. 4, pp. 979–987, Jul. 2004.

Ardashir, J. F., Sabahi, M., Hosseini, S. H., Blaabjerg, F., Babaei, E, and Gharehpetian, G B.," A single-phase transformerless inverter with charge pump circuit concept for grid-tied pv

applications," IEEE Trans. on Industrial electronics, vol. 64, Issue 7, pp. 5403-5417, July 2017.

Hinago, Y., and Koizumi, H.," A Single-Phase Multilevel Inverter Using Switched Series/Parallel DC Voltage Sources," IEEE Trans. on Industrial electronics, vol. 57, no.8, pp. 2643-2650, Aug. 2010.

Fong, Y. C., Cheng, K. W. E., Y. Ye, and Chan, Y. C." centralized regulation scheme for parallel mode switched-capacitor converter system with simple unit commitment," Trans. on Industrial electronics, vol. 57, Issue.8, pp. 6148--6158, Aug. 2017.

McGrath, B. P. and Holmes, D. G., "Multicarrier PWM strategies for multilevel inverters," IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 858–867, Aug. 2002.

Das, S. and Narayanan, G., "Novel switching sequences for a space-vector modulated three-level inverter," IEEE Trans. Ind. Electron., vol. 59, no. 3, pp. 1477–1487, Mar. 2012.

Agelidis, V. G., Balouktsis, A. I., and Cossar, C., "On attaining the multiple solutions of selective harmonic elimination PWM three-level waveforms through function minimization," IEEE Trans. Ind. Electron., vol. 55, no. 3, pp. 996–1004, Mar. 2008.

Hinago, Y. and Koizumi, H., "A modulation method for capacitor voltage ripple reduction of the switched-capacitor inverter using series/ parallel conversion," in Proc. IEEE Int. Conf. Ind. Technol., pp. 105–109, Mar. 2011,